Al giorno d’oggi gli FPGA sono utilizzati in un numero sempre crescente di apparecchiature e produttori di dispositivi offrono anche core di processore da utilizzare all’interno del proprio FPGA.

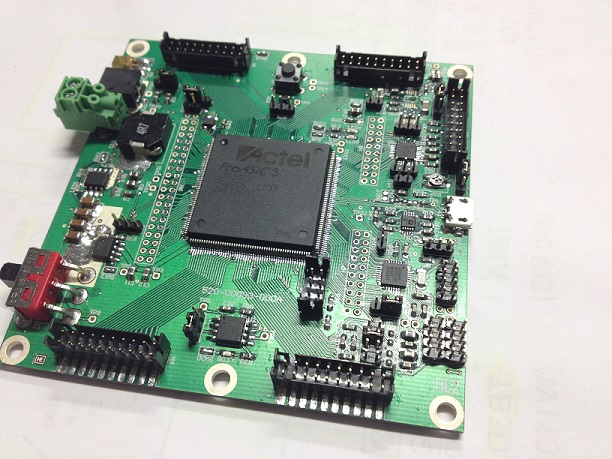

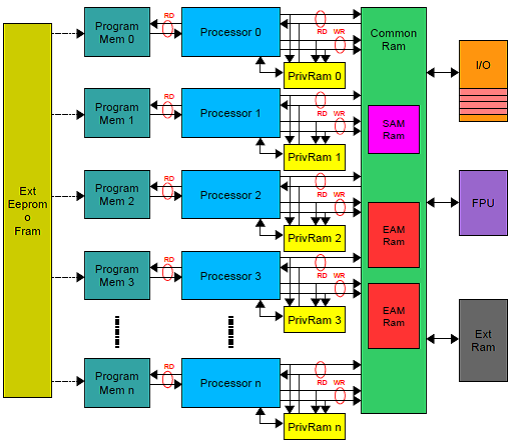

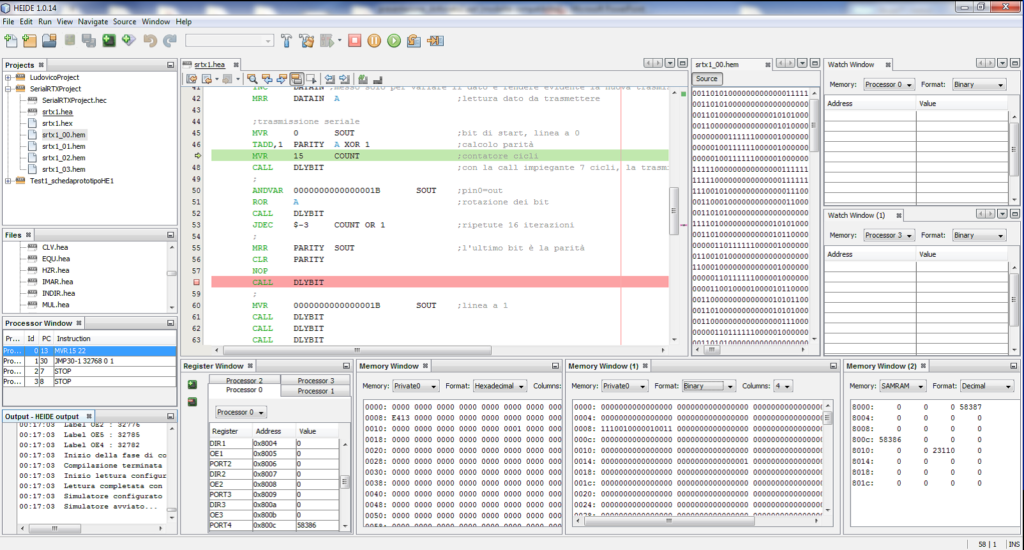

Helabor è una piattaforma multiprocessore, sviluppata interamente in VHDL, implementabile in qualsiasi FPGA.

Il codice VHDL del multiprocessore è completamente parametrizzato in modo da poter dimensionare l’architettura in modo completamente libero e adattarla alle particolari esigenze applicative.

Oltre a costruire il sistema con il numero di processori necessari all’interno di un FPGA, possiamo espandere il multiprocessore utilizzando più FPGA, comunicando processori, contenuti in FPGA distinti, tramite connessioni seriali dedicate (multiprocessor cluster interconnection).